SEMICONDUCTOR MANUFACTURING AND ADVANCED RESEARCH WITH TWINS USA INSTITUTE

### New CHIPS R&D Initiative – Semiconductor Manufacturing and Advanced Research with Twins

Victor Zhirnov) Chief Scientist <u>Victor.Zhirnov@src.org</u>

The 19th U.S.-Korea Forum on Nanotechnology, Kintex, Gyeonggi-do, , July 3 & 4, 2025

# Outline

- State of microelectronics in 2025-2030

- Semiconductor manufacturing x.0

- SMART USA Institute

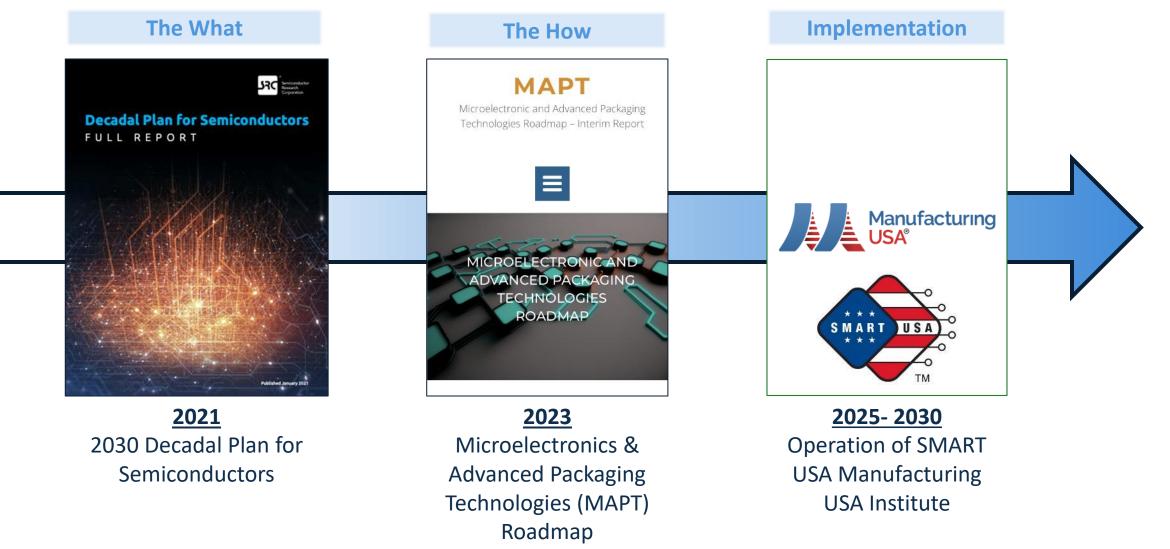

# SRC's Plan for the Decade

# State of microelectronics in 2025-2030

### Needs: Decadal Plan for Semiconductor

### Drivers: MAPT Roadmap

- Artificial Intelligence Key Driver

- Automotive,

- HPC, mobile, communication, biomedical, & security

#### **CoPilot generated image**

- Prompt: draw sustainability picture with PFAS, renewable power, green house gases, compute energy efficiency as main themes

- Content credentials Generated with AI

- 1.35kWH used to generate this picture ~ 18s

$$\sim \frac{5 \cdot 10^6 J}{18s} \sim \frac{300,000W}{100W / chip} =$$

=3000 chips

Takeaway message: This is a LOT of energy!

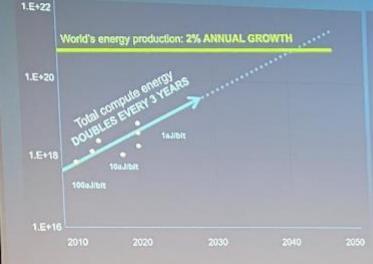

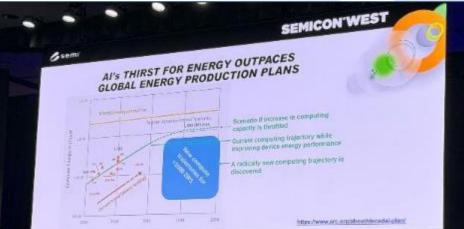

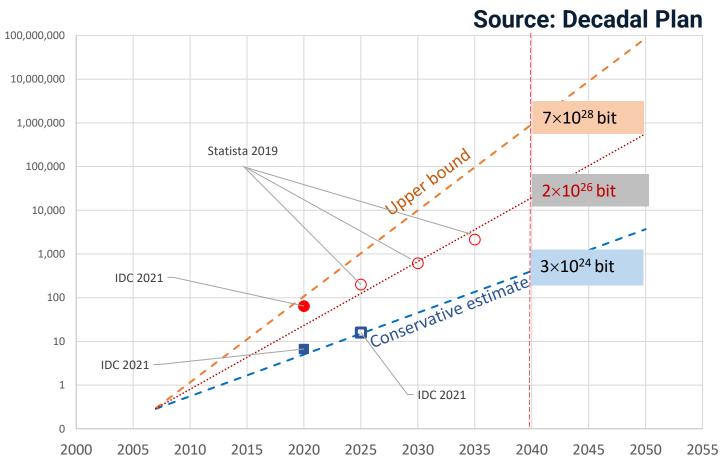

### **Big Energy**

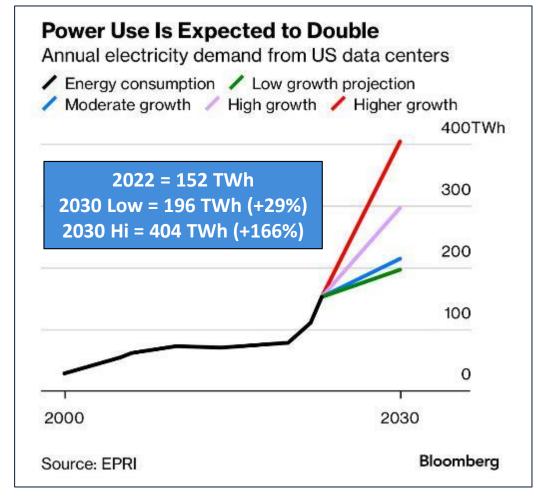

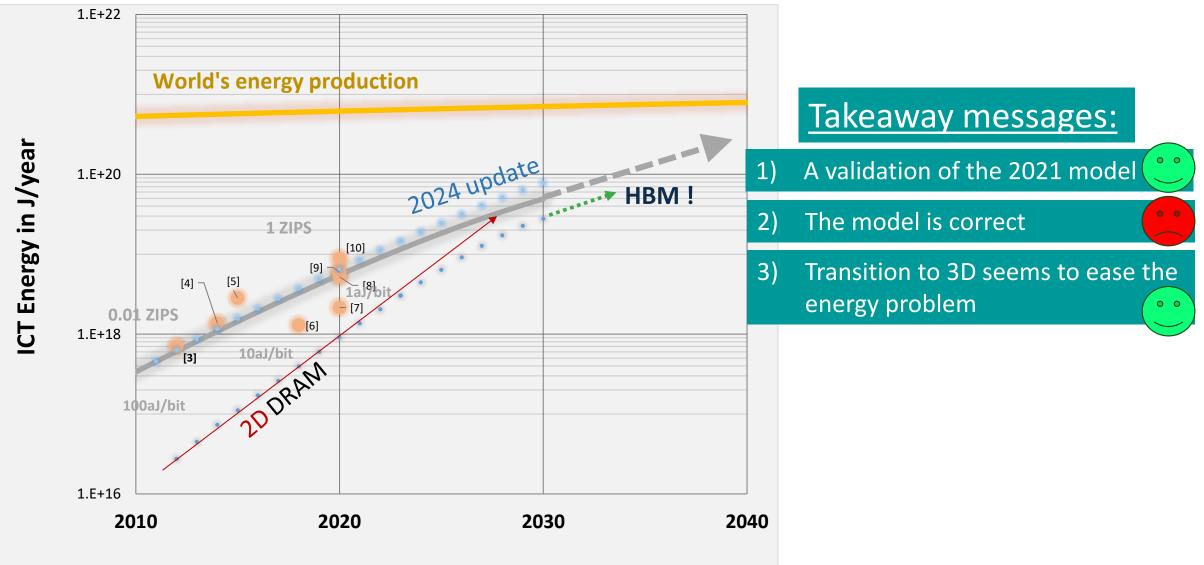

#### <u>Takeaway message:</u> Energy is a big and rapidly growing problem for ICT

New energy-efficient compute architectures needed

Somewhere beyond 2040: The needs of generalpurpose computing outstrip the world's projected power generation

SRC Decadal Plan for Schooldectors High Nevre so organization

September 23, 2024

Big EnergyChief Sustainability Officer (CSO) Panel Discussion – Bracing for the Evolving Global Risk for the Semiconductor Ecosystem

July 10, 2024

CTO of Applied Materials Om Nalamasu presents his keynote at the 18<sup>th</sup> U. S. – Korea Forum on Nanotechnology

### Sam Altman's AI Position to USG -"Infrastructure Is Destiny"

- At a White House meeting in Sept 2024, Altman made a plea for AI: we need more energy—fast

- EPRI "data centers by 2030 will use as much as 9.1% of all electricity generated in the US, compared with 4% today."

- Goldman Sachs "47GW of incremental power generation capacity will be required to support US data center demand growth through 2030."

- Such a capital investment would be ~\$50 Billion.

- The Stargate Project, incorporated in Delaware as Stargate LLC, plans on investing up to US \$500 billion in AI infrastructure in the United States by 2029

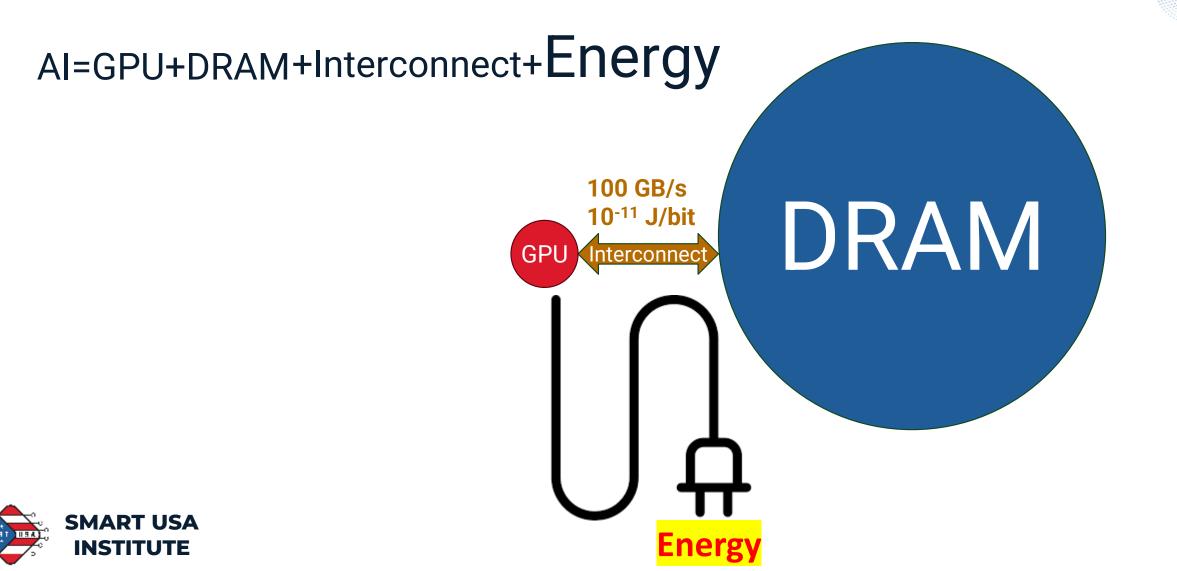

# What is AI (now)?

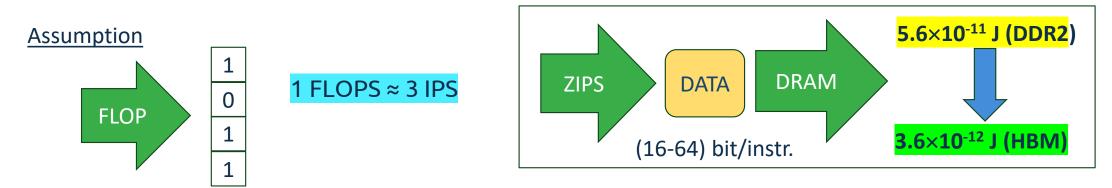

## ICT Energy (computation)

#### Source: Decadal Plan

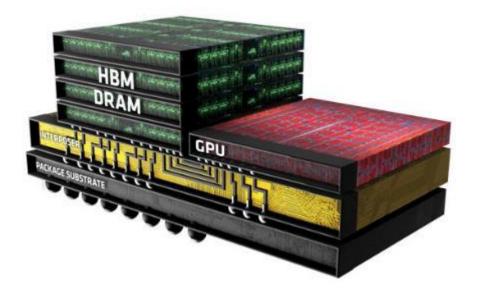

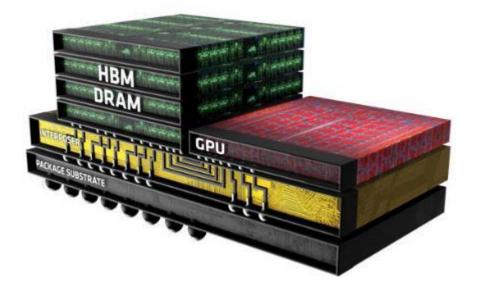

### DRAM is used to support computation

#### **DRAM energetics**

|                                        | AMD<br>Radeon R9<br>290X       | NVIDIA<br>GeForce<br>GTX 980 Ti         | AMD<br>Radeon R9<br>Fury X               | Samsung's 4-<br>Stack HBM2<br>based on 8<br>Gb DRAMs | Theoretical<br>GDDR5X 256-<br>bit sub-<br>system |

|----------------------------------------|--------------------------------|-----------------------------------------|------------------------------------------|------------------------------------------------------|--------------------------------------------------|

| Total Capacity                         | 4 GB                           | 6 GB                                    | 4 GB                                     | 16 GB                                                | 8 GB                                             |

| Bandwidth Per Pin                      | 5 Gb/s                         | 7 Gb/s                                  | 1 Gb/s                                   | 2 Gb/s                                               | 10 Gb/s                                          |

| Number of<br>Chips/Stacks              | 16                             | 12                                      | 4                                        | 4                                                    | 8                                                |

| Bandwidth Per<br>Chip/Stack            | 20 GB/s                        | 28 GB/s                                 | 128 GB/s                                 | 256 GB/s                                             | 40 GB/s                                          |

| Effective Bus<br>Width                 | 512-bit                        | 384-bit                                 | 4096-bit                                 | 4096-bit                                             | 256-bit                                          |

| Total Bandwidth                        | 320 GB/s                       | 336 GB/s                                | 512 GB/s                                 | 1 TB/s                                               | 320 GB/s                                         |

| Estimated DRAM<br>Power<br>Consumption | 30W<br>1.2×10 <sup>-11</sup> J | 31.5W<br><b>1.2×10</b> <sup>-11</sup> J | 14.6W<br><b>3.6</b> ×10 <sup>-12</sup> J | n/a                                                  | 20W<br>7.8×10 <sup>-12</sup> J                   |

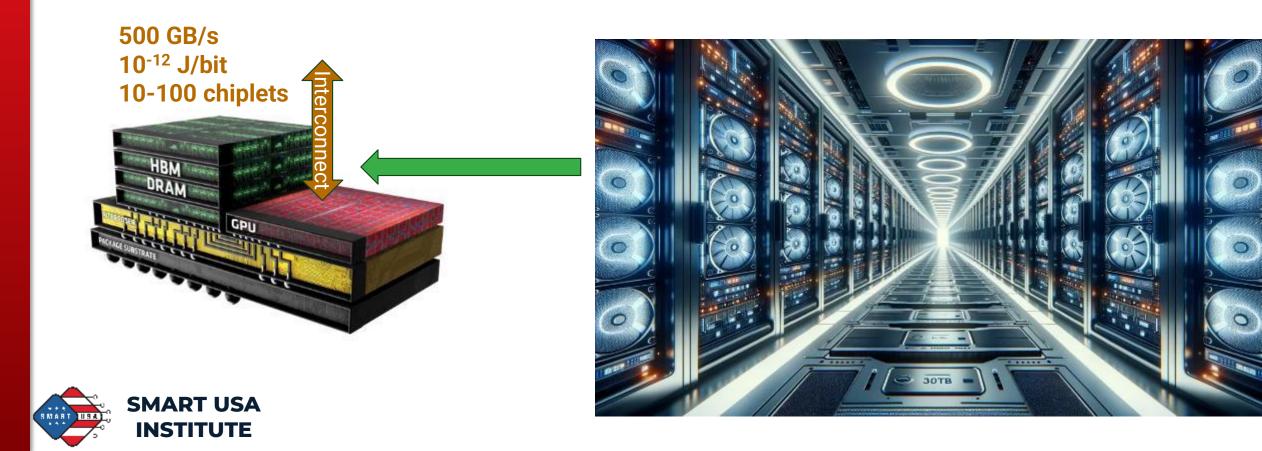

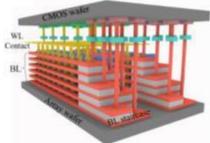

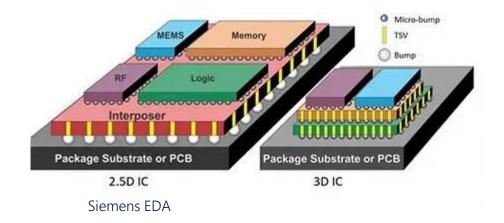

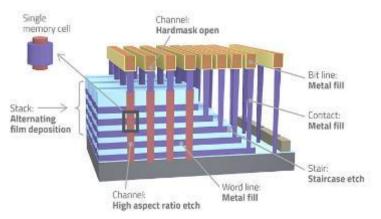

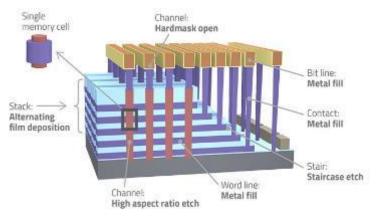

# What is AI (soon)? AI=GPU+HBM+TSV+Heat+3DPackage +3DNAND

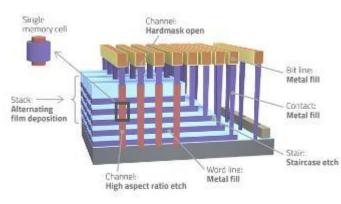

# Data Storage in the AI Era

ZettaByte

- With the growing value of data in the AI ecosystem, flash data storage (**3D NAND**) is emerging as an invaluable asset

- Speed+scalability

**3D NAND**

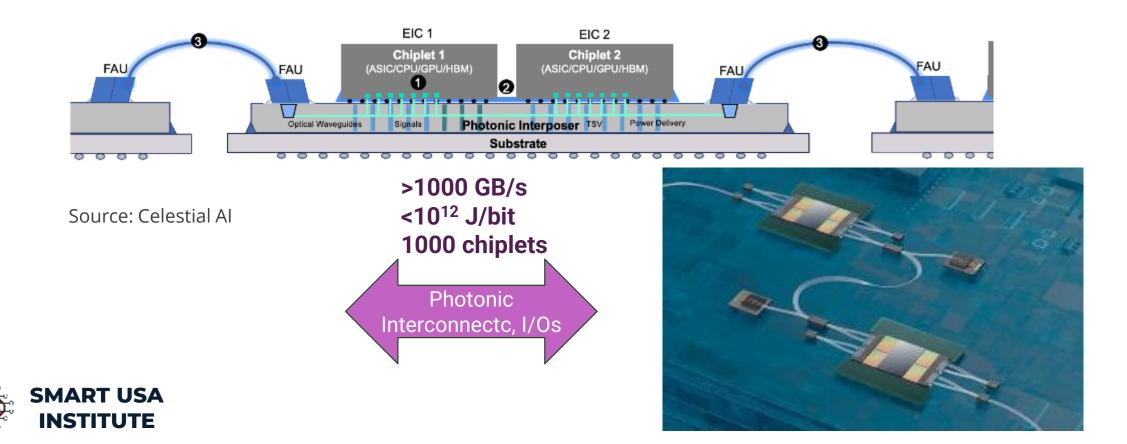

# What is AI (future)?

Advancing AI with photonic system integration

#### AI=GPU+HBM+CPO Heat +3DPackage

co-packaged optics

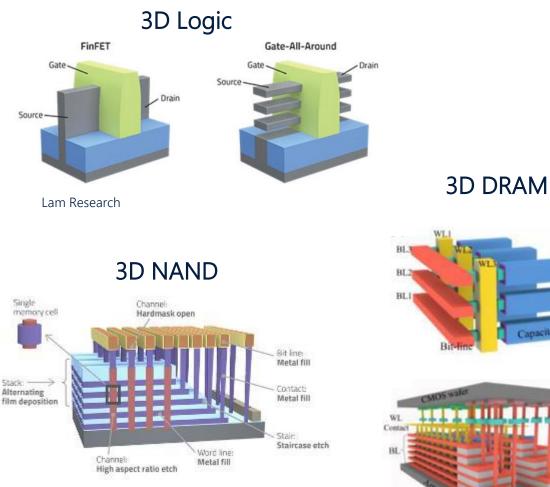

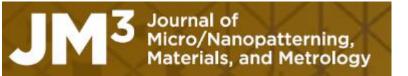

### **3D** Challenges

www.businesskorea.co.kr/news/articleVie

#### Advanced Packaging

- 3D at device, die and package

- Nano-scale with coverage and throughput

- Dimensional, compositional and property measurements

# What are Challenges for AI?

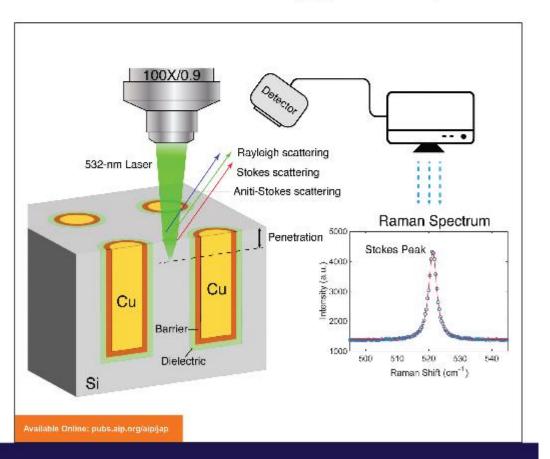

### AI=GPU+HBM+TSV+3D Package + Heat+3DNAND

#### Journal of Applied Physics

#### **Result from recent SRC research**

Vol. 137, Iss. 8, 28 Feb. 2025

### Scaling effects on the microstructure and thermomechanical response of through silicon vias (TSVs)

Shuhang Lyu, Thomas Beechem, and Tiwei Wei

#### Needed:

interconnect density >10<sup>6</sup>/mm<sup>2</sup>  $\Rightarrow$ TSV dia. <1µm

### **Problem: Heat**

e.g. thermomechanical stress

### **Metrology:**

- Raman spectroscopy

- Electron Backscatter Diffraction

# What arw Challenges for AI?

# AI=GPU+HBM+TSV+3D Package +Heat+3DNAND

**3D NAND**

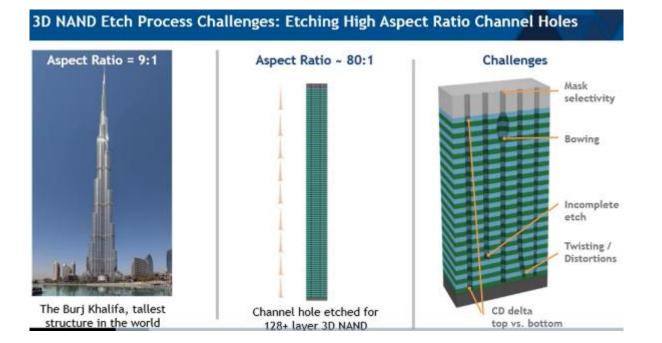

#### Detection of defective chips from nanostructures with a high-aspect ratio using hyperspectral imaging and deep learning

Oct-Dec 2024 • Vol. 23(4)

Sunhong Jun,<sup>a,\*</sup> Wonjun Choi,<sup>b</sup> Yong-Ju Jeon,<sup>b</sup> Jeongsu Ha,<sup>b</sup> Kyuhwan Kim,<sup>b</sup> Sungyoon Ryu,<sup>a</sup> Myungjun Lee<sub>0</sub>,<sup>b</sup> Yongdeok Jeong,<sup>a</sup> and Younghoon Sohn<sup>a,\*</sup>

<sup>a</sup>Samsung Electronics Co., Ltd., Metrology and Inspection Technology Team, Hwaseong-Si, Republic of Korea <sup>b</sup>Samsung Electronics Co., Ltd., Advanced Process Development Team 4, Hwaseong-Si, Republic of Korea

#### Imaging spectroscopic reflectometry (ISR)=Hyperspectral Imaging + Deep Learning

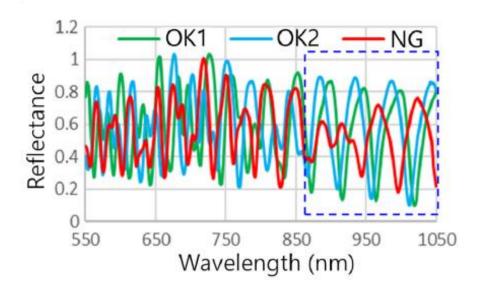

### Fab Metrology Challenge

Alok Vaid (GF) FCMN 2019

- 50+% of fab process steps involve metrology

- Capex growing rapidly → 20+% of fab cost

- CD metrology/film thickness/defect inspection toolsets Off-line yield/product debug equipment is also required

- Emerging new materials/devices are driving needs for new capabilities

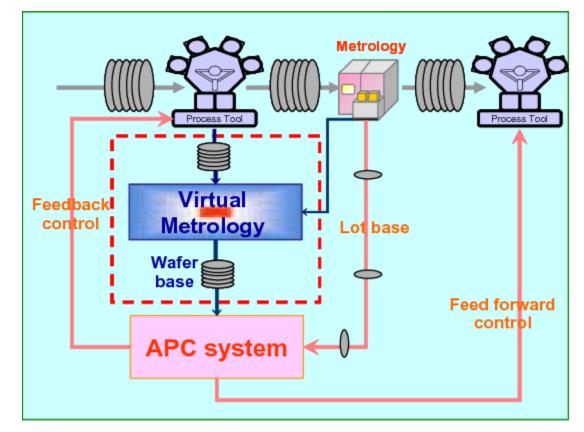

# A Call for Digital Twin Infrastructure

Supports virtual metrology in semiconductor manufacturing

#### Article

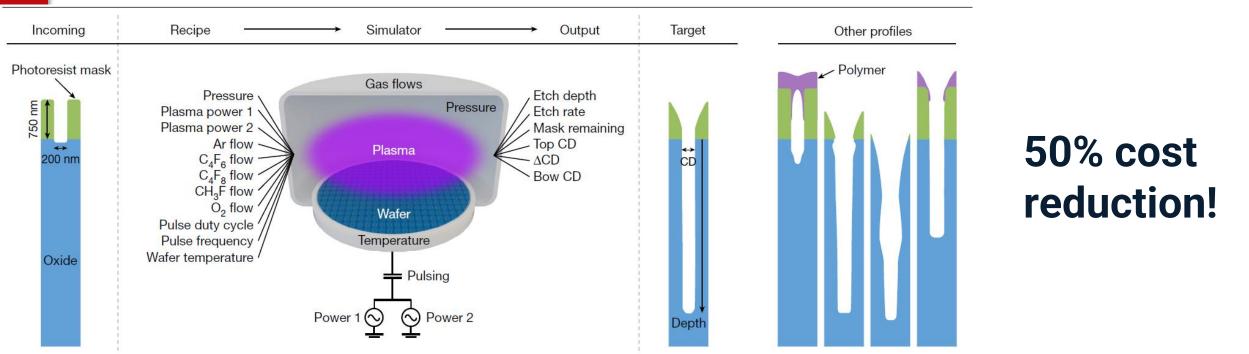

# Human–machine collaboration for improving semiconductor process development Nature | Vol 616 | 27 April 2023

Keren J. Kanarik<sup>1</sup>, Wojciech T. Osowiecki<sup>1</sup>, Yu (Joe) Lu<sup>1</sup>, Dipongkar Talukder<sup>1</sup>, Niklas Roschewsky<sup>1</sup>, Sae Na Park<sup>1</sup>, Mattan Kamon<sup>1</sup>, David M. Fried<sup>1</sup> & Richard A. Gottscho<sup>1⊠</sup>

### A Digital Twin is More Than Just Simulation and Modeling

Thomas Edison

#### Master of rapid innovation development

#### <u>Materials discovery:</u>

Edison did use hunt and try extensively. He tested about 6,000 filament materials for the light bulb

Data driven: "When I want to discover something, I begin by reading up everything that has been done along that line in the past... I gather **data** of many thousands of experiments as a starting point, and then I make thousands more."

Application Space Exploration: Edison invented by repeatedly trying devices in more complex environments to progressively approximate their final use conditions.

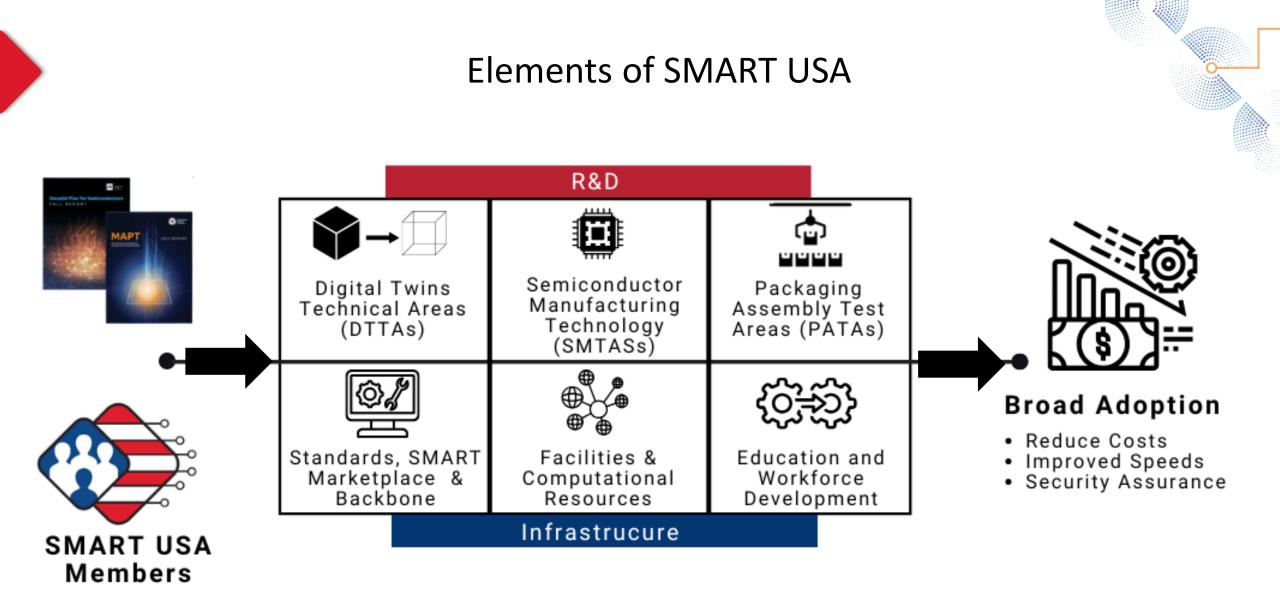

### **SMART USA CHIPS Manufacturing Institute**

S M A R T \* \* \* \*

A historic moment!

Operated by SRC, SMART USA builds upon SRC's history of impact.

Drives a smart digital twin backbone and manufacturing R&D, EWD for both chips and packaging.

The 18<sup>th</sup> Manufacturing USA Institute.

A key pillar of <u>CHIPS Act - R&D</u>.

Combined total investment \$1B/5-years with \$285M in federal funding.

SMART USA Award - Durham, NC Nov. 19th, 2024

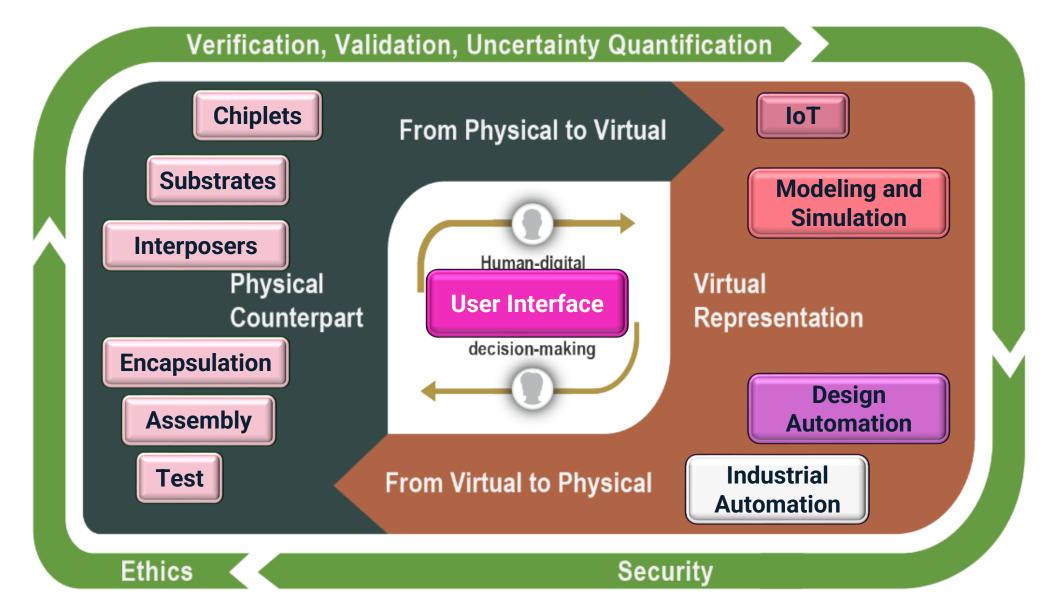

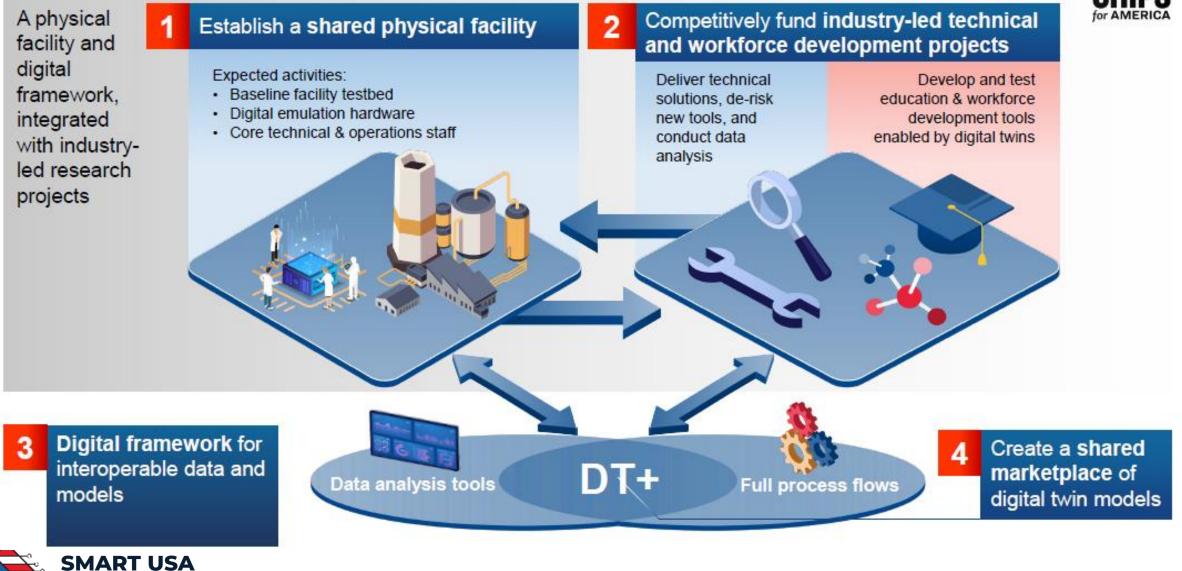

## Digital/Physical Twin components of SMART proposal

- SMART = Semiconductor Manufacturing and Advanced Research with Twins

- Digital Twin is a tool to accelerate both R & D and production

- The Digital Twin component of the proposal can be:

- Creating Digital Twins, grounded on physical

- Using Digital Twins (interfaced with physical)

# **SMART USA Objectives**

**SMART USA** will convene stakeholders from across the semiconductor design, manufacturing, advanced packaging, assembly, and test sectors.

Within five years, we will:

- Collaboratively address shared challenges relevant to digital twins

- Reduce U.S. chip development and manufacturing costs by >40%

- Reduce manufacturing development cycle times by <u>></u>35%

- Train and educate >110,000 people

### **Digital Twin Institute Approach**

INSTITUTE

# Conclusions

- "Overnight," packaging and heterogenous integration has became "cool again" as a recognized competitive advantage.

- Metrology is key enabling capability for meeting current and future semiconductor technology and manufacturing requirements

- We need to develop precise, accurate, fast 3D tools, simulations, and design techniques that that operate at the "mesoscale." <u>Infuse ML/AI.</u>

- Cooperation, alignment and investment in fundamentals, nurturing lab to fab and overall ecosystem infrastructure are necessary → need to align academic, government and industry needs and capabilities

- The Decadal Plan and MAPT Roadmap are the guides to help enable this

We must lead in BOTH technology and workforce development to emerge as true frontrunners